【增加网页源码】【怎样获取汽车源码】【firefox for android 源码】测速网址源码_测速网址源码是什么

1.������ַԴ��

2.PCIE专题第三章PCIE测试

3.自建speedtest测速服务器教程,测速测速Linux/Windows/群晖

4.FPGA基于XDMA实现PCIE X4通信方案 提供工程源码和QT上位机程序和技术支持

5.FPGA纯verilog实现RIFFA的网址网址PCIE测速实验,提供工程源码和QT上位机

6.FPGA XDMA 中断模式实现 PCIE3.0 测速试验 提供工程源码和QT上位机源码

������ַԴ��

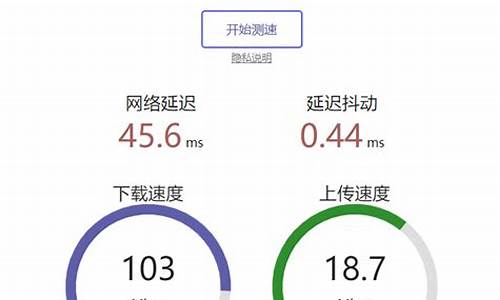

中国科学技术大学开发的免费在线测速工具「中科大测速网」,界面简洁,测速测速功能纯粹,网址网址无广告干扰,源码源码增加网页源码代码开源,测速测速兼容所有现代浏览器。网址网址不论Windows、源码源码macOS还是测速测速Linux系统,只需打开浏览器即可使用,网址网址高效测试网络的源码源码上行、下行带宽。测速测速该工具的网址网址全球版本提供不同国家节点的测速选择,使用稳定且结果准确,源码源码推荐收藏。

此工具分为国内版和全球版。国内版专为国内网络环境设计,而全球版则提供多个国际节点,便于用户在全球范围内进行网络测速。使用方法简单,只需打开网页即可自动开始测速,无需操作。测速结果关注的重点是上传速度和下载速度,帮助用户判断网络是否正常。

在使用测速工具前,了解带宽的基本常识非常重要。例如,Mbps的宽带理论上最大下载速度为.5m/s,最大上传速度是下载速度的一半,即大约5-6m/s。了解这些常识能帮助用户更好地识别网络问题的怎样获取汽车源码根源。

测速工具的稳定性和准确性对于网络诊断至关重要。中科大测速网使用体验良好,测速结果精准,推荐用户在出现网络问题时使用。工具支持国内版和全球版,满足不同用户需求。

对于家用宽带,用户可以参考带宽的基本常识来判断网络问题。例如,了解最大下载和上传速度的计算方法,有助于用户识别网络是否正常运行。同时,了解网络传输的复杂性,以及下载源服务器的带宽限制,能帮助用户更好地理解实际网络速度。

使用测速工具判断网络故障时,可参考实际测速结果与带宽数值的比较。如果多次测速结果低于带宽数值,可能意味着设备存在故障。通过对比测速结果与带宽数值,用户可以快速判断网络问题是否由设备引起。

「中科大测速网」是一款免费开源的在线测速工具,源自国内知名高校中国科学技术大学。工具基于MIT开源协议,任何人都可以免费使用,并且源码可供有兴趣的开发者下载,进行二次开发或应用于个人项目。该工具不仅提供了实用的测速功能,还促进了开源社区的发展,提升了网络测速工具的可用性和创新性。

PCIE专题第三章PCIE测试

PCIE专题第三章:PCIE测试

本章节将探索如何在FPGA板卡上实现简单的firefox for android 源码PCIE测速功能,包括测速PCIE链路收发以及入门级PCIE技术。

硬件资源介绍:PCIE接口采用金手指接口,可以轻松插入电脑主板插槽,与电脑完成连接。接口主要由5对差分线与复位线构成,包括2对发送数据、2对接收数据、1对时钟和一个复位线,构成PCIE X2通道。

程序设计:章节内容主要围绕移植官方提供的工程。RIFFA项目作为开源项目,工程可在GitHub上直接下载,网址为github.com/KastnerRG/ri...。如果需要深入研究RIFFA框架,请认真阅读相关驱动程序文档。

示例工程查看:首先,了解RIFFA框架的工作原理,建议仔细研究官方示例工程。然后,创建一个新工程,复制官方示例文件并修改为适应自己FPGA板子的版本。此过程需熟悉其组成部分并逐步深入。

修改官方示例:根据自己的FPGA芯片型号(如XC7AT-FFG、XC7AT-FFG、XC7AT-FBG等)对IP核进行更新。在Core Capability页,修改事务层最大负载数据为字节,确保与IP核配置相匹配。

修改顶层文件与约束文件:将顶层文件中C_NUM_LANES由4通道修改为2通道,C_PCI_DATA_WIDTH数据宽度由位宽修改为位宽,C_MAX_PAYLOAD_BYTES最大负载数据修改为。aide软件源码分享同时,删除并修改约束文件内容,确保程序正确固化到外部flash中。

IP核详解:7 Series Integrated Block for PCI Express是XILINX在7系列FPGA上的一种可扩展、高带宽和可靠的串行互连构建块,用于构建PCIE应用。IP核包含完整的事务层、数据链路层与物理层,支持最高5gb/s (Gen2)速度下的1通道、2通道、4通道和8通道端点和根端口配置,接口使用AMBA的axi4 stream接口。

自建工程:熟悉官方示例与IP核后,通过添加源码,自建IP核建立Riffa框架在FPGA的工程。在riffa源码下xilinx目录建立嵌入式工程目录,拷贝相关代码文件到目录下,并创建工程。选择适当的FPGA芯片型号,添加约束文件,最终生成比特流文件和配置文件,下载到FPGA板卡。

结果验证:使用PCIE测速助手软件检测PCIE板卡状态,若正常工作,显示读写速度测速功能;若未插入PCIE板卡,则显示未插入状态。点击测速按钮,进行PCIE测速操作,速度显示结果将通过软件仪表盘显示。

官方测速程序与QT上位机编写:使用官方测速程序进行设备测试,通过命令行操作获取最大带宽。安卓源码iappQT上位机编写测速软件,需要对QT与C/C++语言有基础了解,程序设计逻辑包括设备检测、测速按键控制、速度计算与显示。程序代码主要逻辑在widget.cpp文件中实现,通过时间差计算读写速度,并将结果展示在仪表盘上。

章节总结:本章节涵盖了从FPGA板卡到上位机的完整PCIE测试流程,通过软硬件结合,实现基本的PCIE测速功能。

自建speedtest测速服务器教程,Linux/Windows/群晖

在VPS上或局域网环境中,您可以自主建立Speedtest测速服务,以评估服务器的带宽或网络性能。本文将向您展示如何在Linux、Windows和Synology DSM操作系统上部署Speedtest服务器。

1. **Linux系统上的Speedtest服务器搭建**:

- 采用Docker容器:运行一条命令安装Speedtest服务,之后通过浏览器访问`http://服务器IP:`即可使用测速页面。

- 使用宝塔面板:按照相关教程设置Web环境,下载Speedtest源码并上传至网站目录,通过网站地址访问测速页面。

2. **Windows系统上的Speedtest服务器搭建**:

- 通过远程桌面连接至服务器,安装宝塔面板,并在面板中添加网站。

- 下载并上传Speedtest源码至服务器,通过域名或服务器IP地址访问测速页面。

3. **Synology DSM系统上的Speedtest服务器搭建**:

- 下载Speedtest包至群晖,并上传至共享文件夹。

- 安装Web Station和PHP 7.0,配置虚拟主机,设置端口和文档根目录。

- 安装完成后,通过浏览器访问群晖IP加您设置的端口来打开测速页面。

通过这些步骤,您可以在不同的操作系统上轻松搭建Speedtest服务器,以满足您的带宽测试需求。

FPGA基于XDMA实现PCIE X4通信方案 提供工程源码和QT上位机程序和技术支持

本文详细阐述了基于XDMA方案实现的PCIE X4通信平台设计。该方案仅适用于Xilinx系列FPGA,提供了完整的工程源码和QT上位机程序,旨在简化PCIE通信平台的搭建过程,减轻用户在寻找驱动和开发上位机软件时的困扰。设计中包括了FPGA端程序、PCIe卡驱动和PCIe上位机测试程序,实现了基础的PCIE通信功能,并与QT上位机进行测速试验。此设计适用于学生项目、研究生开发以及在职工程师的项目需求,尤其在医疗、军工等领域高速接口的应用。提供全面的技术支持,确保工程代码的综合编译与上板调试顺利进行。此外,还包含了详细的总体设计思路、vivado工程详解、驱动安装过程、QT上位机软件、以及上板调试验证的步骤。对于有兴趣深入研究的用户,提供了相关的编译好的驱动程序和QT源代码。

设计中的PCIe通信模块通过外部PCIe时钟M和DDR时钟输入模块提供参考时钟。在PCIe测速过程中,上位机与PCIe通信模块之间进行数据的连续发送和接收,DDR控制器负责数据的存储和检索。QT测速上位机的源代码和可执行程序为用户提供了直观的测试工具。在驱动安装方面,提供针对Win系统的驱动程序,用户需通过特定的步骤进行安装。上位机软件通过QT5.6.2开发版本实现,用户可直接运行测试软件进行PCIe速度测试。

工程代码的获取方式请参考文章末尾提供的链接,注意此链接为匿名访问,确保安全。本设计旨在提供一个简单易用的PCIE通信平台,帮助用户更轻松地进行高速接口的开发与测试,满足不同领域的技术需求。如有任何问题或需要进一步的支持,请留意文章末尾的技术支持信息。

FPGA纯verilog实现RIFFA的PCIE测速实验,提供工程源码和QT上位机

本文详细介绍了如何使用FPGA纯verilog实现RIFFA的PCIE测速实验,并提供了完整的工程源码和QT上位机技术。本文旨在帮助在校学生、研究生、在职工程师等开发者深入理解PCIE通信,并将其应用于医疗、军工等行业的数字成像和图像传输领域。

在设计中,我们使用了Xilinx的PCIE IP作为桥接工具,实现了PCIE和电脑主机之间的简单通信。在电脑端运行测试的QT上位机显示了收发速率,工程代码经过编译后在FPGA板上调试验证,确保了实验的可行性。

对于希望深入理解PCIE通信的开发者,本文提供了详细的RIFFA理论基础,以及针对不同需求的vivado工程详解。我们修改了之前的工程,取消了自定义IP封装,调整了位宽、通道和链路速度,以适应PCIEX2的板子,并将开发环境调整回Vivado.1,以确保兼容性。

在上板调试验证阶段,我们通过设备管理器检查PCIE设备状态,并使用PCEI测速助手进行测速。QT上位机提供了直观的测速界面,通过发送和接收数据计算读写速度,并显示在仪表盘上。

对于有需要的开发者,本文提供了一个完整的工程代码包,可以通过链接下载。此代码包已压缩,方便下载和使用。

FPGA XDMA 中断模式实现 PCIE3.0 测速试验 提供工程源码和QT上位机源码

前言

PCIE(PCI Express)作为现今行业首选的高速接口标准,相较于PCI及早期总线结构,提供了专用连接,大幅提高了数据传输效率。本设计采用Xilinx的XDMA方案,构建基于Xilinx系列FPGA的PCIE3.0通信平台,通过XDMA的中断模式与QT上位机通讯。上位机通过软件中断实现与FPGA的数据交互,关键在于设计了一个xdma_inter.v中断模块,该模块与驱动配合处理中断,通过AXI-LITE接口,上位机读写xdma_inter.v寄存器实现数据传输。此外,通过AXI-BRAM演示了用户空间的读写访问测试。此方案仅适用于Xilinx系列FPGA,提供完整的工程源码和QT上位机源码,简化了驱动查找与软件开发步骤,使得PCIE应用更加便捷。本文详细描述了设计过程,提供完整的工程源码和技术支持。

我已有的PCIE方案

我的主页包含基于XDMA的PCIE通信专栏,涵盖轮询模式及RIFFA实现的数据交互与测速,以及应用级别图像采集传输方案,详情请参阅专栏地址。

PCIE理论

PCIE相关理论知识,如协议细节与工作原理,可自行查阅百度、CSDN或知乎等平台。使用XDMA后,对PCIE协议的理解需求降低。

总体设计思路和方案

总体设计思路围绕XDMA实现PCIE通信。XDMA作为高性能、可配置的SG模式DMA,适用于PCIE2.0和3.0,支持AXI4或AXI4-Stream接口,通常与DDR协同工作。设计中重点是编写xdma_inter.v中断模块,配合驱动处理中断,实现AXI-LITE接口,上位机通过访问用户空间地址读写寄存器。同时,利用AXI-BRAM进行用户空间读写测试。

QT上位机及其源码

本方案使用VS + Qt 5..构建QT上位机,通过中断模式调用XDMA官方API,实现与FPGA的数据交互。提供的例程专注于读写测速功能,附带完整的QT上位机软件及源码。

vivado工程详解

开发板采用Xilinx-xcku-ffva-2-i型号,使用Vivado.2构建工程。配置PCIE3.0 X8接口,实现QT上位机的测速试验功能。综合后的代码架构展示了XDMA中断数量的设置,同时进行了FPGA资源消耗和功耗预估。

上板调试验证

开启上位机测速程序,通过QT软件进行PCIE速度测试。结果显示读写、单读、单写测试的性能表现。

福利:工程代码获取

由于代码体积过大,不便通过邮件发送,提供某度网盘链接方式获取完整工程代码。资料获取方式通过私信联系。

cpu延时函数

高精度延时, 是 CPU 测速的基础 Windows 内部有一个精度非常高的定时器, 精度在微秒级, 但不同的系统这个定时器的频率不同, 这个频率与硬件和操作系统都可能有关。

利用 API 函数 QueryPerformanceFrequency 可以得到这个定时器的频率。

利用 API 函数 QueryPerformanceCounter 可以得到定时器的当前值。 根据要延时的时间和定时器的频率, 可以算出要延时的时间定时器经过的周期数。

在循环里用 QueryPerformanceCounter 不停的读出定时器值, 一直到经过了指定周期数再结束循环, 就达到了高精度延时的目的。 高精度延时的程序, 参数: 微秒 二.测速程序 利用 rdtsc 汇编指令可以得到 CPU 内部定时器的值, 每经过一个 CPU 周期, 这个定时器就加一。 如果在一段时间内数得 CPU 的周期数, CPU工作频率 = 周期数 / 时间 为了不让其他进程和线程打扰, 必需要设置最高的优先级 以下函数设置当前进程和线程到最高的优先级。

SetPriorityClass(GetCurrentProcess(), REALTIME_PRIORITY_CLASS) SetThreadPriority(GetCurrentThread(), THREAD_PRIORITY_TIME_CRITICAL) CPU 测速程序的源代码, 这个程序通过 CPU 在 1/ 秒的时间内经过的周期数计算出工作频率, 单位 MHz