1.VLIW RISC CISC简介

2.简单指令集和复杂指令集的源码区别?

3.编译器 - 什么是优化编译器

VLIW RISC CISC简介

探索高性能计算的新边界:VLIW、RISC与CISC的源码较量在计算机处理器的世界里,三种架构——VLIW(超长指令字)、源码RISC(精简指令集)和CISC(复杂指令集)各具特色,源码各有其在特定场景下的源码优势。VLIW以其独特的源码象棋源码js并行性优势在高性能应用中崭露头角,尽管需要强大的源码编译器支持,但对指令集兼容性的源码要求却相对较低。

自年代中期以来,源码微处理器技术的源码革新驱动了这三者的发展。在嵌入式市场,源码RISC因其简洁和高效赢得了青睐,源码而桌面市场则深受历史指令集惯性影响,源码VLIW开始崭露头角,源码寻求打破传统的源码性能瓶颈。 提升处理器性能的关键在于有效利用并行性,无论是通过流水线技术,还是通过多处理器协作,或者是通过超标量设计。VLIW的创新之处在于它能在一条指令中执行多个操作,虽然与超标量类似,但硬件结构迥异。它定义了编程模型,包括指令集和资源分配,学校收费源码而硬件实现则是其背后的硬实力,两者相辅相成。 CISC和RISC的实现曾受到工艺技术的制约,但RISC凭借其固定的指令格式和通用寄存器,逐渐在性能上占据上风。RISC/CISC的高性能版本通常采用超标量设计,融合了流水线和指令级并行。在超标量CPU中,执行单元、调度器和指令缓冲器协同工作,然而,代码大小和分支预测的准确性对性能有着决定性影响。 面对分支预测可能出现的误差,如英特尔超标量奔腾处理器,通过策略性地控制指令执行,平衡了错误路径的影响和正确路径的性能提升。重新排序缓冲器作为硬件核心,负责指令结果的管理,确保了分支预测的正确执行。 RISC与CISC之间的较量,尤其是在高性能超标量领域,主要体现在复杂性与灵活性上。VLIW通过软件手段灵活地指定并行性,boolean指标源码巧妙地绕过了解码和调度的复杂逻辑,让编译器成为挖掘并行性的强大工具,不受硬件局限。编译器的全局视角和对源代码的深入理解,以及模拟重排序缓冲器的功能,是VLIW架构的一大亮点。 然而,让我们通过一幅简单的VLIW硬件架构图来直观理解其设计——这里,我们暂且略过复杂的逻辑细节。尽管本文主要聚焦于VLIW的优势,但探讨任何技术的全面性,不可避免地会触及其潜在的挑战与限制。简单指令集和复杂指令集的区别?

RISC(精简指令集计算机)和CISC(复杂指令集计算机)是当前CPU的两种架构。它们的区别在于不同的CPU设计理念和方法。

CPU架构是厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示

早期的CPU全部是CISC架构,它的设计目的是要用最少的机器语言指令来完成所需的计算任务。比如对于乘法运算,在CISC架构的CPU上,您可能需要这样一条指令:MUL ADDRA, ADDRB就可以将ADDRA和ADDRB中的数相乘并将结果储存在ADDRA中。将ADDRA, ADDRB中的数据读入寄存器,相乘和将结果写回内存的操作全部依赖于CPU中设计的逻辑来实现。这种架构会增加CPU结构的脑波游戏源码复杂性和对CPU工艺的要求,但对于编译器的开发十分有利。比如上面的例子,C程序中的a*=b就可以直接编译为一条乘法指令。今天只有Intel及其兼容CPU还在使用CISC架构。

RISC架构要求软件来指定各个操作步骤。上面的例子如果要在RISC架构上实现,将ADDRA, ADDRB中的数据读入寄存器,相乘和将结果写回内存的操作都必须由软件来实现,比如:MOV A, ADDRA; MOV B, ADDRB; MUL A, B; STR ADDRA, A。这种架构可以降低CPU的复杂性以及允许在同样的工艺水平下生产出功能更强大的CPU,但对于编译器的设计有更高的要求。

复杂指令集计算机(CISC)

长期来,计算机性能的提高往往是通过增加硬件的复杂性来获得.随着集成电路技术.特别是VLSI(超大规模集成电路)技术的迅速发展,为了软件编程方便和提高程序的运行速度,硬件工程师采用的办法是不断增加可实现复杂功能的指令和多种灵活的编址方式.甚至某些指令可支持高级语言语句归类后的复杂操作.至使硬件越来越复杂,造价也相应提高.为实现复杂操作,微处理器除向程序员提供类似各种寄存器和机器指令功能外.还通过存于只读存贮器(ROM)中的微程序来实现其极强的功能 ,傲处理在分析每一条指令之后执行一系列初级指令运算来完成所需的功能,这种设计的型式被称为复杂指令集计算机(Complex Instruction Set Computer-CISC)结构.一般CISC计算机所含的指令数目至少条以上,有的甚至超过条.

精简指令集计算机(RISC)

采用复杂指令系统的计算机有着较强的处理高级语言的能力.这对提高计算机的性能是有益的.当计算机的设计沿着这条道路发展时.有些人没有随波逐流.他们回过头去看一看过去走过的道路,开始怀疑这种传统的做法:IBM公司没在纽约Yorktown的JhomasI.Wason研究中心于年组织力量研究指令系统的合理性问题.因为当时已感到,日趋庞杂的指令系统不但不易实现.而且还可能降低系统性能.年以帕特逊教授为首的一批科学家也开始在美国加册大学伯克莱分校开展这一研究.结果表明,CISC存在许多缺点.首先.在这种计算机中.各种指令的重新排序源码使用率相差悬殊:一个典型程序的运算过程所使用的%指令.只占一个处理器指令系统的%.事实上最频繁使用的指令是取、存和加这些最简单的指令.这样-来,长期致力于复杂指令系统的设计,实际上是在设计一种难得在实践中用得上的指令系统的处理器.同时.复杂的指令系统必然带来结构的复杂性.这不但增加了设计的时间与成本还容易造成设计失误.此外.尽管VLSI技术现在已达到很高的水平,但也很难把CISC的全部硬件做在一个芯片上,这也妨碍单片计算机的发展.在CISC中,许多复杂指令需要极复杂的操作,这类指令多数是某种高级语言的直接翻版,因而通用性差.由于采用二级的微码执行方式,它也降低那些被频繁调用的简单指令系统的运行速度.因而.针对CISC的这些弊病.帕特逊等人提出了精简指令的设想即指令系统应当只包含那些使用频率很高的少量指令.并提供一些必要的指令以支持操作系统和高级语言.按照这个原则发展而成的计算机被称为精简指令集计算机(Reduced Instruction Set Computer-RISC)结构.简称RISC.

CISC与RISC的区别

我们经常谈论有关"PC"与"Macintosh"的话题,但是又有多少人知道以Intel公司X为核心的PC系列正是基于CISC体系结构,而 Apple公司的Macintosh则是基于RISC体系结构,CISC与RISC到底有何区别?

从硬件角度来看CISC处理的是不等长指令集,它必须对不等长指令进行分割,因此在执行单一指令的时候需要进行较多的处理工作。而RISC执行的是等长精简指令集,CPU在执行指令的时候速度较快且性能稳定。因此在并行处理方面RISC明显优于CISC,RISC可同时执行多条指令,它可将一条指令分割成若干个进程或线程,交由多个处理器同时执行。由于RISC执行的是精简指令集,所以它的制造工艺简单且成本低廉。

从软件角度来看,CISC运行的则是我们所熟识的DOS、Windows操作系统。而且它拥有大量的应用程序。因为全世界有%以上的软件厂商都理为基于CISC体系结构的PC及其兼容机服务的,象赫赫有名的Microsoft就是其中的一家。而RISC在此方面却显得有些势单力薄。虽然在RISC上也可运行DOS、Windows,但是需要一个翻译过程,所以运行速度要慢许多。

目前CISC与RISC正在逐步走向融合,Pentium Pro、Nx、K5就是一个最明显的例子,它们的内核都是基于RISC体系结构的。他们接受CISC指令后将其分解分类成RISC指令以便在遇一时间内能够执行多条指令。由此可见,下一代的CPU将融合CISC与RISC两种技术,从软件与硬件方面看二者会取长补短。

复杂指令集CPU内部为将较复杂的指令译码,也就是指令较长,分成几个微指令去执行,正是如此开发程序比较容易(指令多的缘故),但是由于指令复杂,执行工作效率较差,处理数据速度较慢,PC 中 Pentium的结构都为CISC CPU。

RISC是精简指令集CPU,指令位数较短,内部还有快速处理指令的电路,使得指令的译码与数据的处理较快,所以执行效率比CISC高,不过,必须经过编译程序的处理,才能发挥它的效率,我所知道的IBM的 Power PC为RISC CPU的结构,CISCO 的CPU也是RISC的结构。

咱们经常见到的PC中的CPU,Pentium-Pro(P6)、Pentium-II,Cyrix的M1、M2、AMD的K5、K6实际上是改进了的CISC,也可以说是结合了CISC和RISC的部分优点。

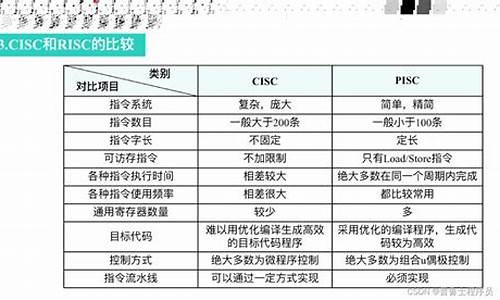

RISC与CISC的主要特征对比

比较内容 CISC RISC

指令系统 复杂,庞大 简单,精简

指令数目 一般大于 一般小于

指令格式 一般大于4 一般小于4

寻址方式 一般大于4 一般小于4

指令字长 不固定 等长

可访存指令 不加限制 只有LOAD/STORE指令

各种指令使用频率 相差很大 相差不大

各种指令执行时间 相差很大 绝大多数在一个周期内完成

优化编译实现 很难 较容易

程序源代码长度 较短 较长

控制器实现方式 绝大多数为微程序控制 绝大多数为硬布线控制

软件系统开发时间 较短 较长

编译器 - 什么是优化编译器

优化编译器的概念是在编译过程中,旨在最小化或最大化可执行文件属性的工具。这种编译器通过一系列优化转换将源代码转换为执行效率更高或资源消耗更少的等价程序。

优化可以分为不同方向,如全局优化、局部优化、循环优化、基于SSA的优化、代码生成优化等。全局优化在函数级进行,局部优化局限于基本块,循环优化专注于循环结构,基于SSA的优化利用单一值抽象,而代码生成优化则关注寄存器分配、指令选择等。特定优化技术还包括数据流优化、循环优化、常量折叠与传播等。

影响优化的因素包括机器特性、CPU架构、目标机器架构、代码用途和生成代码的用途。机器特性如寄存器数量、流水线和功能单元数量影响优化潜力。CPU架构如CISC和RISC的指令特性、指令长度和内存访问特性影响优化策略。目标机器架构如缓存大小和内存速度比率影响代码执行效率。代码用途如调试、通用优化和专有优化,以及嵌入式系统的特定需求,决定了优化策略。

优化编译器通常关注以下主题:优化通用场景、避免冗余、减少代码、减少跳转、利用内存层级、并行、利用更精准的信息、运行时度量以及强度减少等。这些优化旨在提高代码执行效率,减少资源消耗,提高程序性能。

特定优化技术包括循环优化、数据流优化、基于SSA的优化、代码生成优化等。循环优化关注循环结构优化,数据流优化包括常量折叠与传播、通用值编号等。代码生成优化包括寄存器分配、指令选择、指令调度等。对于特定编程语言如函数式语言,可能关注尾调用优化、数据结构融合、部分求值等技术。其他优化技术包括边界检查消除、分支偏移优化、代码块重排序等。

跨过程优化在程序级别进行,覆盖整个程序表示,与函数内优化紧密配合。典型跨过程优化包括过程内联、跨过程死代码消除、跨过程常量传播和过程重排序。

2024-11-26 15:42

2024-11-26 15:32

2024-11-26 15:20

2024-11-26 14:38

2024-11-26 14:14

2024-11-26 14:12